$$\frac{A/2 - acuster}{2ming}$$

$$\frac{A/2 - acuster}{2ming}$$

$$\frac{B/2 - acuster}$$

4

9-1

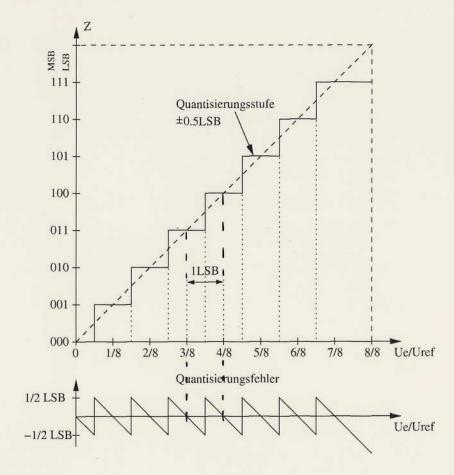

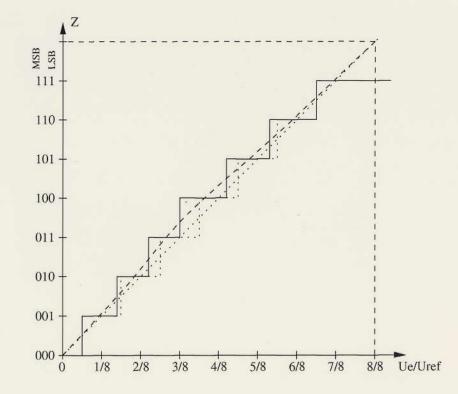

# Ideale Kennlinie eines 3Bit-Wandlers

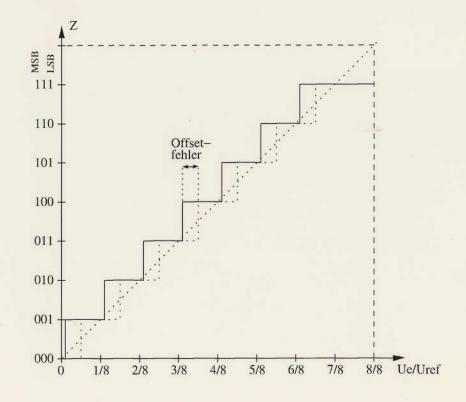

# Offsetfehler

.

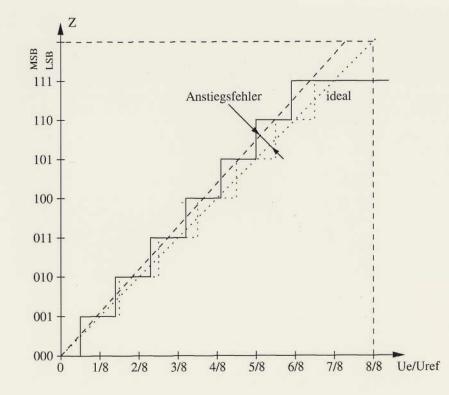

# Verstärkungsfehler

# Integrale Nichtlinearität

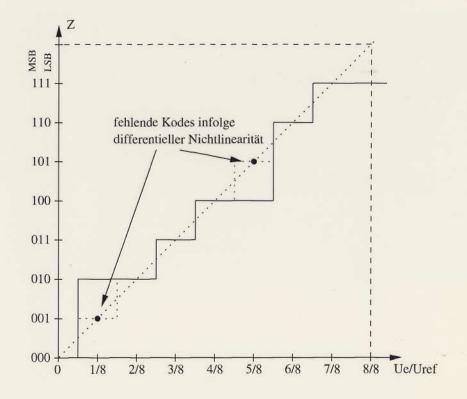

# Differentielle Nichtlinearität

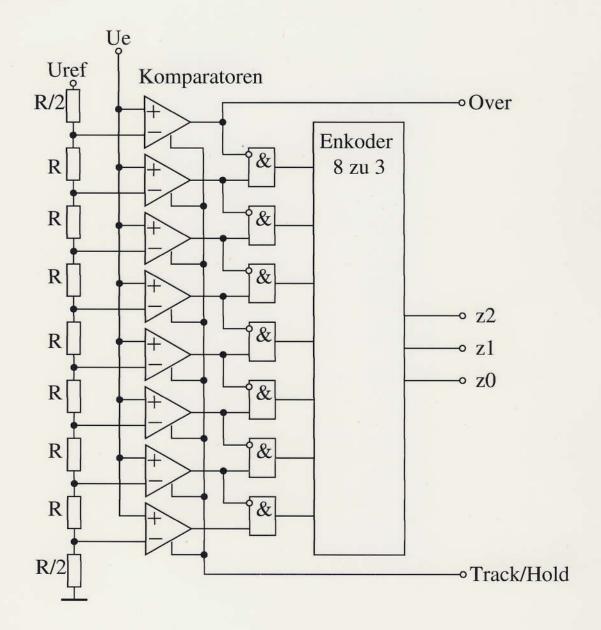

Parallelwandler

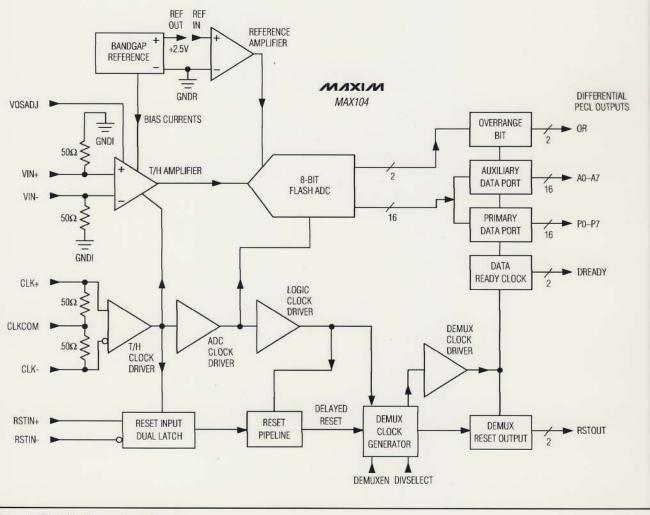

## ±5V, 1Gsps, 8-Bit ADC with **On-Chip 2.2GHz Track/Hold Amplifier**

Figure 1. Simplified Functional Diagram

## **Detailed Description**

The MAX104 is an 8-bit, 1Gsps flash analog-to-digital converter (ADC) with on-chip track/hold (T/H) amplifier and differential PECL-compatible outputs. The ADC (Figure 1) employs a fully differential 8-bit quantizer and a unique encoding scheme to limit metastable states to typically one error per 1016 clock cycles, with no error exceeding 1LSB max.

An integrated 8:16 output demultiplexer simplifies interfacing to the part by reducing the output data rate to one-half the sampling clock rate. This demultiplexer has internal reset capability that allows multiple MAX104s to be time-interleaved to achieve higher effective sampling rates.

When clocked at 1Gsps, the MAX104 provides a typical effective number of bits (ENOB) of >7.5 bits at an analog input frequency of 500MHz. The analog input of the MAX104 is designed for differential or single-ended use with a ±250mV full-scale input range. In addition, this ADC features an on-chip +2.5V precision bandgap reference. If desired, an external reference can also be used.

MIXIM

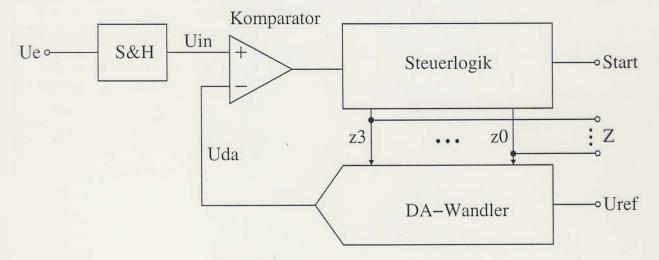

## Wandler mit sukzessiver Approximation

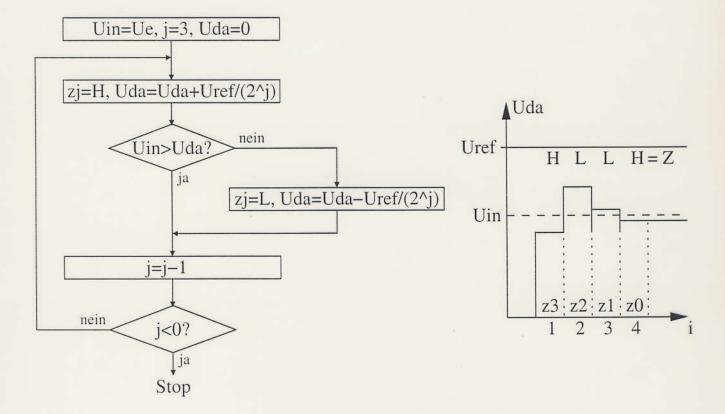

# +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs

## **Detailed Description**

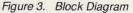

The MAX146/MAX147 analog-to-digital converters (ADCs) use a successive-approximation conversion technique and input track/hold (T/H) circuitry to convert an analog signal to a 12-bit digital output. A flexible serial interface provides easy interface to microprocessors ( $\mu$ Ps). Figure 3 is a block diagram of the MAX146/MAX147.

#### Pseudo-Differential Input

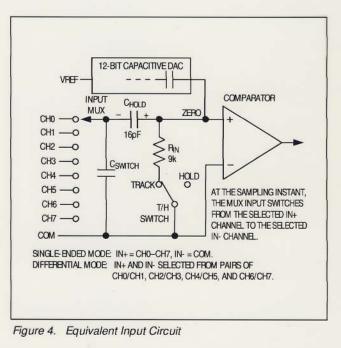

The sampling architecture of the ADC's analog comparator is illustrated in the equivalent input circuit (Figure 4). In single-ended mode, IN+ is internally switched to CH0–CH7, and IN- is switched to COM. In differential mode, IN+ and IN- are selected from the following pairs: CH0/CH1, CH2/CH3, CH4/CH5, and CH6/CH7. Configure the channels with Tables 2 and 3.

In differential mode, IN- and IN+ are internally switched to either of the analog inputs. This configuration is pseudo-differential to the effect that only the signal at IN+ is sampled. The return side (IN-) must remain stable within  $\pm 0.5$ LSB ( $\pm 0.1$ LSB for best results) with respect to AGND during a conversion. To accomplish this, connect a  $0.1\mu$ F capacitor from IN- (the selected analog input) to AGND.

During the acquisition interval, the channel selected as the positive input (IN+) charges capacitor C<sub>HOLD</sub>. The acquisition interval spans three SCLK cycles and ends

on the falling SCLK edge after the last bit of the input control word has been entered. At the end of the acquisition interval, the T/H switch opens, retaining charge on  $C_{HOLD}$  as a sample of the signal at IN+.

The conversion interval begins with the input multiplexer switching C<sub>HOLD</sub> from the positive input (IN+) to the negative input (IN-). In single-ended mode, IN- is simply COM. This unbalances node ZERO at the comparator's input. The capacitive DAC adjusts during the remainder of the conversion cycle to restore node ZERO to 0V within the limits of 12-bit resolution. This action is equivalent to transferring a 16pF x [(V<sub>IN+</sub>) - (V<sub>IN</sub>-)] charge from C<sub>HOLD</sub> to the binary-weighted capacitive DAC, which in turn forms a digital representation of the analog input signal.

#### Track/Hold

The T/H enters its tracking mode on the falling clock edge after the fifth bit of the 8-bit control word has been shifted in. It enters its hold mode on the falling clock edge after the eighth bit of the control word has been shifted in. If the converter is set up for single-ended inputs, IN- is connected to COM, and the converter samples the "+" input. If the converter is set up for differential inputs, IN- connects to the "-" input, and the difference of |IN+ - IN-| is sampled. At the end of the conversion, the positive input connects back to IN+, and C<sub>HOLD</sub> charges to the input signal.

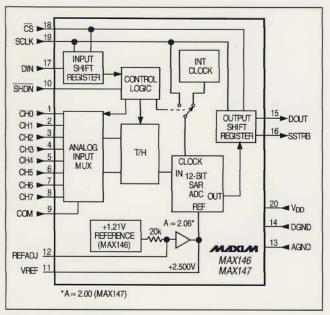

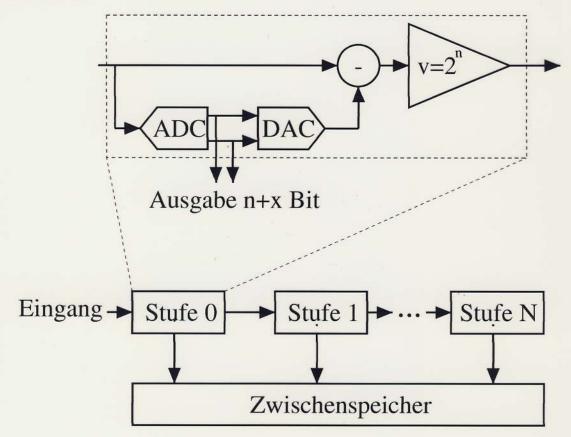

Pipeline AD-Wandler

# +5V Single-Supply, 1Msps, 16-Bit Self-Calibrating ADC

## Detailed Description

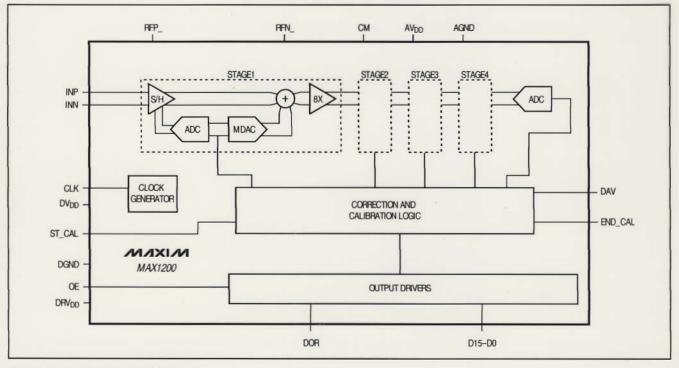

## **Converter Operation**

The MAX1200 is a 16-bit, monolithic analog-to-digital converter (ADC) capable of conversion rates up to 1Msps. It uses a multistage, fully differential, pipelined architecture with digital error correction and self-calibration to provide typically 91dB spurious-free dynamic range at a 1Msps sampling rate. It also provides excellent SNR and THD performance up to the Nyquist frequency. This makes the device suitable for applications such as data acquisition, high-resolution imaging, scanners, digital communication, and instrumentation.

Figure 1 shows the simplified, internal structure of the ADC. A switched-capacitor, pipelined architecture is used to digitize the signal at a high throughput rate. The first four stages of the pipeline use a low-resolution quantizer to approximate the input signal. The multiplying digital-to-analog converter (MDAC) stage is used to subtract the quantized analog signal from the input. The residue is then amplified with a fixed gain and passed on to the next stage. The accuracy of the converter is improved by a digital calibration algorithm which corrects for mismatches between the capacitors in the switched-capacitor MDAC. Note that the pipeline

introduces latency of four sampling periods between the input being sampled and the output appearing at D15-D0.

While the device can handle both single-ended or differential inputs (see the *Requirements for Reference and Analog Signal Inputs* section), the latter mode of operation will guarantee best THD and SFDR performance. The differential input provides the following advantages compared to a single-ended operation:

- Twice as much signal input span

- Common-mode noise immunity

- · Virtual elimination of the even-order harmonics

- Less stringent requirements on the input signal processing amplifiers

## Requirements for Reference and Analog Signal Inputs

MAXIM

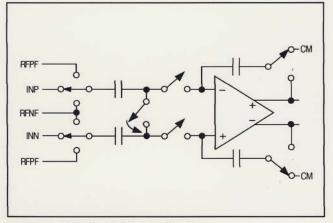

Fully differential switched-capacitor circuits (SC) are used for both the reference and analog inputs (Figure 2). This allows either single-ended or differential signals to be used in the reference and/or analog signal paths. The signal voltage on these pins (INP, INN, RFP\_, RFN\_) should never exceed the analog supply rail, AV<sub>DD</sub>, nor fall below ground.

Figure 1. Internal Functional Diagram

# +5V Single-Supply, 1Msps, 16-Bit Self-Calibrating ADC

Figure 2. Simplified MDAC Architecture

## Choice of Reference

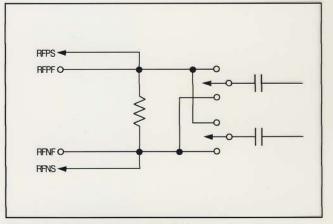

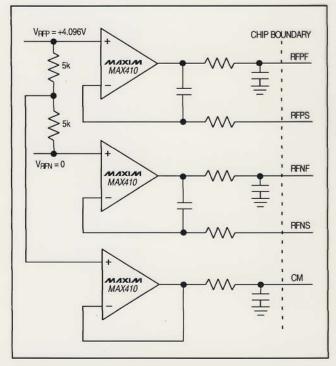

It is important to choose a low-noise reference such as the MAX6341, which can provide both excellent load regulation and low temperature drift. The equivalent input circuit for the reference pins is shown in Figure 3. Note that the reference pins drive approximately 1k $\Omega$  of resistance on-chip. They also drive a switched capacitor of 21pF. To meet the dynamic performance, the reference voltage is required to settle to 0.0015% within one clock cycle. Carefully choose an appropriate driving circuit (Figure 4). The capacitors at the reference pins (RFPF, RFNF) provide the dynamic charge required during each clock cycle, while the op amps ensure accuracy of the reference signals. These capacitors must have low dielectric-absorption characteristics, such as polystyrene or teflon capacitors.

The reference pins can be connected to either singleended or differential voltages within the specified maximum levels. Typically the positive reference pin (RFPF) would be driven to +4.096V, and the negative reference pin (RFNF) connected to analog ground for best SNR performance. If THD performance is more important to the application than signal-to-noise ratio, choose a lower level, differential voltage such as V<sub>RFPS</sub> = +3.5V and V<sub>RFNS</sub> = +1.5V.

There are sense pins, RFPS and RFNS, which can be used with external amplifiers to compensate for any resistive drop on these lines, internal or external to the chip. Ensure a correct reference voltage by using proper Kelvin connections at the sense pins.

### Common-Mode Voltage

The switched-capacitor input circuit at the analog input allows signals between AGND and the analog power supply. Since the common-mode voltage has a strong

**WIXIW**

Figure 3. Equivalent Input at the Reference Pins. The sense pins should not draw any DC current.

Figure 4. Drive Circuit for Reference Pins and Common-Mode Pin

influence on the performance of the ADC, the best results are obtained by choosing V<sub>CM</sub> = (V<sub>RFPS</sub> + V<sub>RFNS</sub>) / 2. This can be achieved by using a resistive divider between the two reference potentials. Figure 4 shows a typical driving circuit for good dynamic performance.

9

1AX1200

9-4

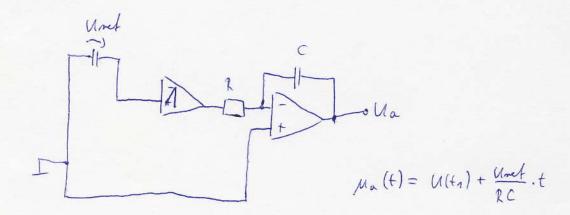

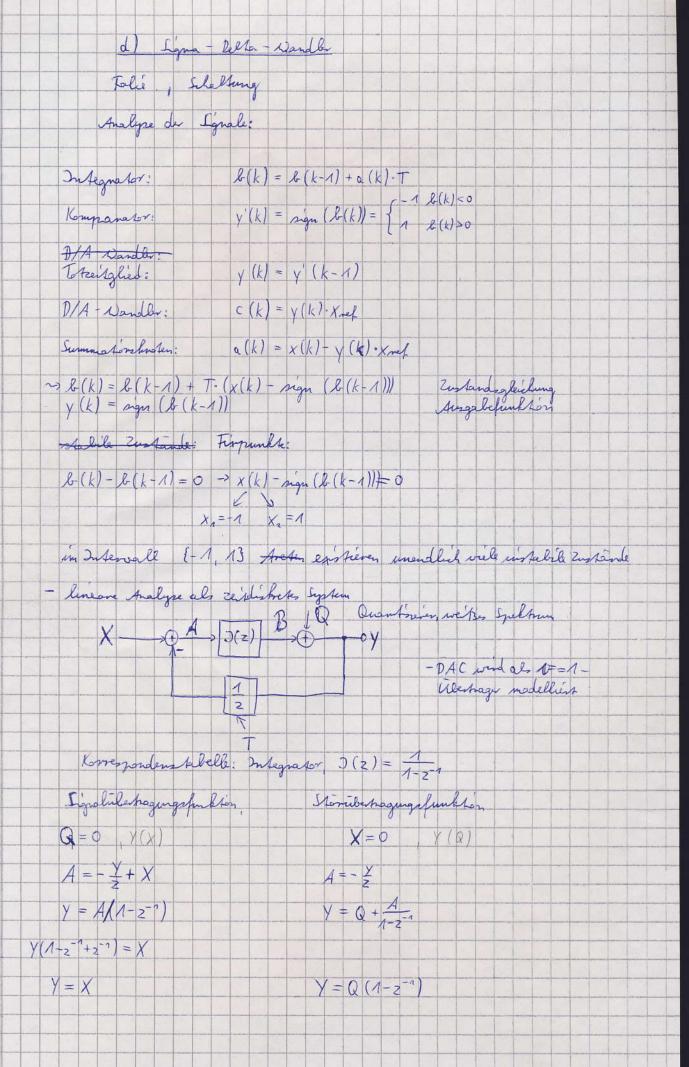

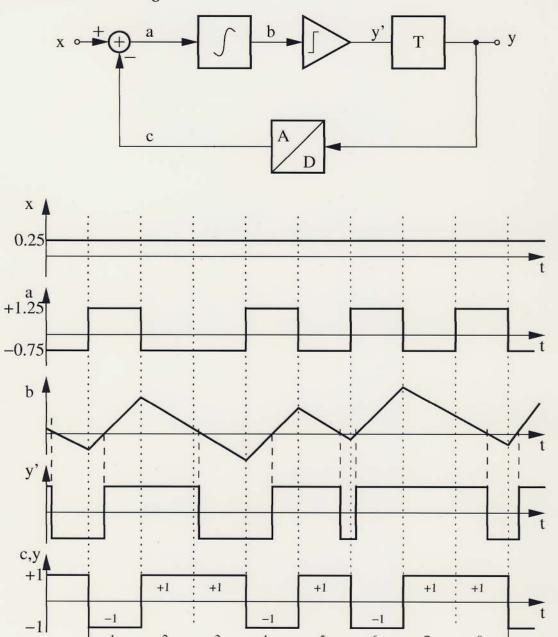

## Sigma-Delta-Wandler 1. Ordnung

$[5^{*}(+1) + 3^{*}(-1)]/8 = 0.25$

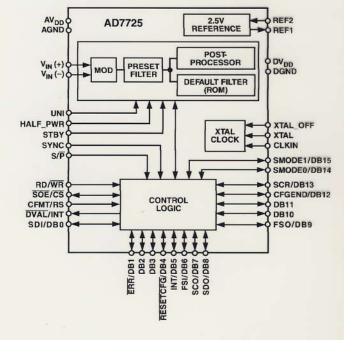

# 16-Bit 900 kSPS $\Sigma$ - $\Delta$ ADC with a Programmable Postprocessor

# AD7725

#### FEATURES

Programmable Filtering: Any Characteristic up to 108 Tap FIR and/or IIR Polynomial Signal Conditioning up to 8th Order Programmable Decimation and Output Word Rate Flexible Programming Modes: Boot from DSP or External EPROM Parallel/Serial Interface Internal Default Filter for Evaluation 14.4 MHz Max Master Clock Frequency 0 V to +4 V (Single-Ended) or ±2 V (Differential) Input Range Power Supplies: AV<sub>DD</sub>, DV<sub>DD</sub>: 5 V ± 5% **On-Chip 2.5 V Voltage Reference** 44-Lead MQFP Package TYPICAL APPLICATIONS Radar

Sonar Auxiliary Car Functions Medical Communications

#### FUNCTIONAL BLOCK DIAGRAM

#### GENERAL DESCRIPTION

The AD7725 is a complete 16-bit,  $\Sigma$ - $\Delta$  analog-to-digital converter with on-chip, user-programmable signal conditioning. The output of the modulator is processed by three cascaded finite impulse response (FIR) filters, followed by a fully user-programmable postprocessor. The postprocessor provides processing power of up to 130 million accumulates (MAC) per second. The user has complete control over the filter response, the filter coefficients, and the decimation ratio.

The postprocessor permits the signal conditioning characteristics to be programmed through a parallel or serial interface. It is programmed by loading a user-defined filter in the form of a configuration file. This filter can be loaded from a DSP or an external serial EPROM. It is generated using a digital filter design package called Filter Wizard, which is available from the AD7725 section on the Analog Devices website. Filter Wizard allows the user to design different filter types and generates the appropriate configuration file to be downloaded to the postprocessor. The AD7725 also has an internal default filter for evaluation purposes.

It provides 16-bit performance for input bandwidths up to 350 kHz with an output word rate of 900 kHz maximum. The input sample rate is set either by the crystal oscillator or an external clock.

This part has an accurate on-chip 2.5 V reference for the modulator. A reference input/output function allows either the internal reference or an external system reference to be used as the reference source for the modulator.

The device is available in a 44-lead MQFP package and is specified over a  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

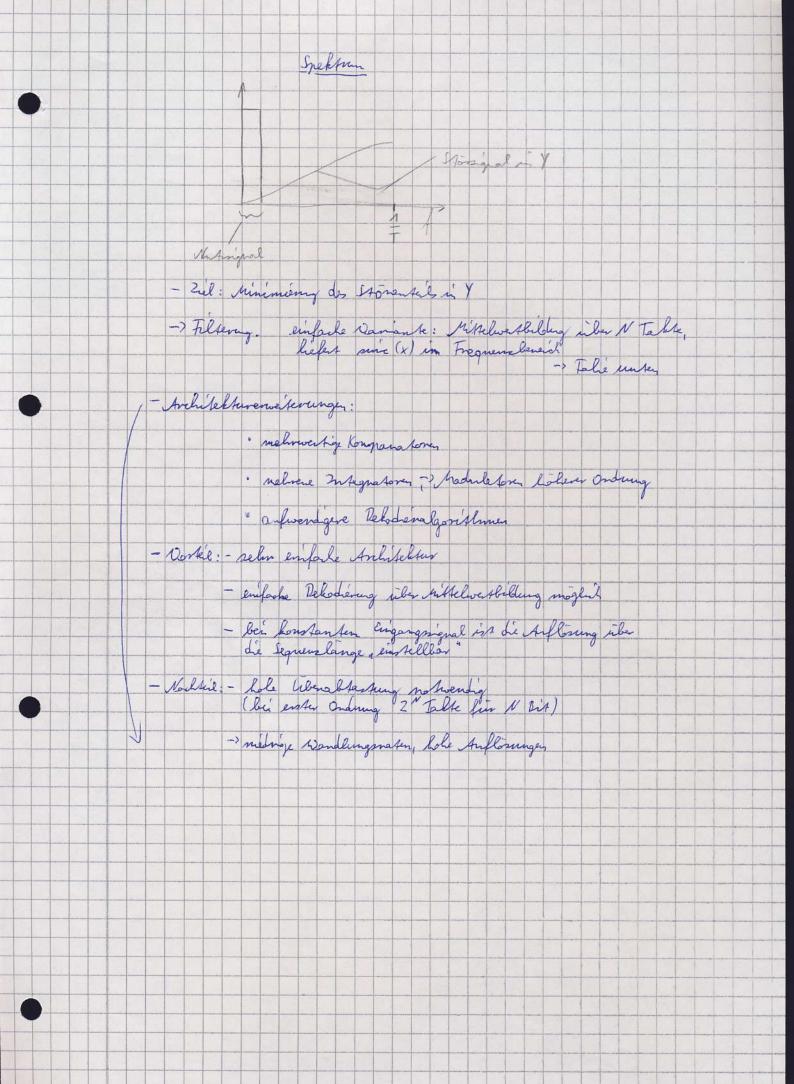

-> Tolie

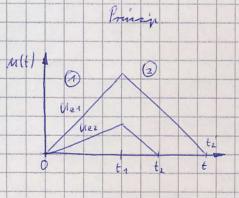

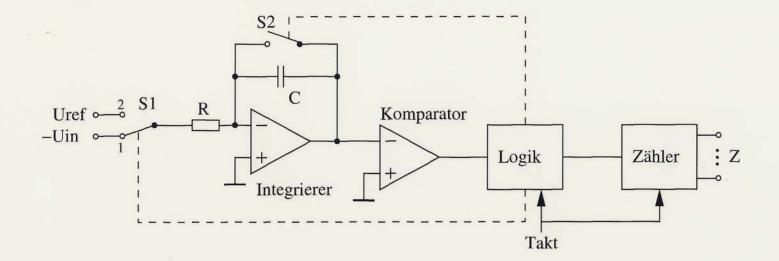

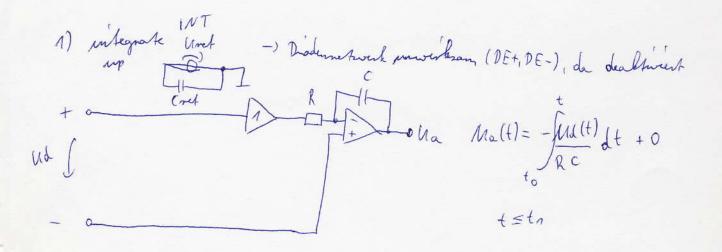

Aufintegreisen der Eingengesmannung über eine feste Zeit to, Con lie 0

3 Abintegriesen mit Unit - C2 = houst. Mensen der Zeit t2-ta ~ Ule

- dunk mitignation während to wicht der wande Mittelwatteilleit, kein S & H an Erigng witig

- Einstellung der Integnationseit to -> Stäruntendreichung, 2. B. Umtridreichung von Nehlbrunnen möglich

Einsach: represent

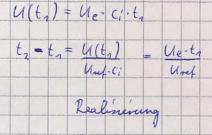

# **Dual-Slope Wandler**

19-0009; Rev 2; 8/95 EVALUATION KIT MANUAL

FOLLOWS DATA SHEET

# MIXIM ±18-Bit ADC with Serial Interface

## General Description

The MAX132 is a CMOS, 18-bit plus sign, serial-output, analog-to-digital converter (ADC). Multi-slope integration provides high-resolution conversions in less time than standard integrating ADCs, allowing operation up to 100 conversions per second. Low conversion noise provides guaranteed operation with ±512mV full-scale input range (2µV/LSB). A simple 4-wire serial interface connects easily to all common microprocessors, and twos-complement output coding simplifies bipolar measurements. Typical supply current is only 60µA and is reduced to 1µA in sleep mode. Four serially programmed digital outputs can be used to control an external multiplexer or programmable-gain amplifier. The MAX132 comes in 24-pin narrow DIP and wide SO packages, and is available in commercial and extended temperature grades.

High resolution, compact size, and low power make this device ideal for data loggers, weigh scales, data-acquisition systems, and panel meters.

## Applications

**Remote Data Acquisition**

**Battery-Powered Instruments**

Industrial Process Control

Transducer-Signal Measurement Pressure, Flow, Temperature, Voltage Current, Resistance, Weight

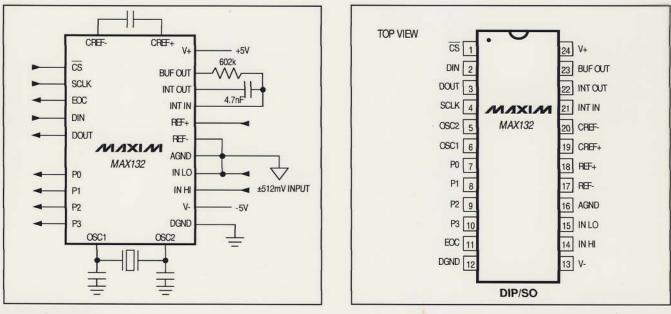

## Functional Diagram

Features

- Low Supply Current: 60µA (Normal Operation) 1µA (Sleep-Mode Operation)

- ±0.006% FSR Accuracy at 16 Conv/sec

- Low Noise: 15µVRMS

- Serial I/O Interface with Programmed Output for Mux and PGA

- Performs up to 100 Conv/sec

- ±2pA Input Current

- 50Hz/60Hz Rejection

## **Ordering Information**

| PART      | TEMP. RANGE      | PIN-PACKAGE           |

|-----------|------------------|-----------------------|

| MAX132CNG | 0 ℃ to +70 ℃     | 24 Narrow Plastic DIP |

| MAX132CWG | 0°C to +70°C     | 24 Wide SO            |

| MAX132C/D | 0℃ to +70℃       | Dice*                 |

| MAX132ENG | -40 ℃ to +85 ℃   | 24 Narrow Plastic DIP |

| MAX132EWG | -40 °C to +85 °C | 24 Wide SO            |

| MAX132MRG | -55℃ to +125℃    | 24 Narrow CERDIP**    |

Contact factory for dice specifications.

\*\* Contact factory for availability and processing to MIL-STD-883.

## Pin Configuration

## **MIXIM**

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

# ±18-Bit ADC with Serial Interface

$\pm 660$ mV for 60Hz mode operation or between  $\pm 390$ mV and  $\pm 550$ mV for 50Hz mode operation. The pseudodifferential input voltage is applied across pins 14 and 15 (IN HI, IN LO), and can range to within 2V of either supply rail.

The inputs IN HI and IN LO lead directly to CMOS transistor gates, yielding extremely high input impedances that are useful when converting signals from a high input source impedance, such as a sensor. Input currents are only 2pA typical at +25 °C. Figure 6 shows an RC filter at the input to optimize noise performance. Fault protection is accomplished by the 100k $\Omega$  series resistance. Internal protection diodes, which clamp the analog inputs from V+ to V-, allow the channel input pins to swing from (V- - 0.3V) to (V+ + 0.3V) without damage. However, if the analog input voltage at the pins IN HI or IN LO exceed the supplies, limit the current into the device to less than 1mA, as excessive current will damage the device.

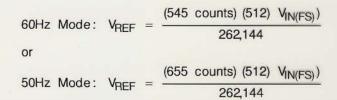

#### Reference Voltage Selection

The reference voltage sets the analog input voltage range. For the nominal  $\pm$ 512mV full-scale input range, a 545mV reference voltage is used for the 60Hz mode and a 655mV reference voltage is used in the 50Hz mode. The reference voltage can be calculated as follows:

The recommended reference voltage range is 500mV to 700mV. The MAX132 is tested with the nominal 545mV reference voltage in 60Hz mode. Use amplifiers or attenuators (resistor dividers) to scale other full-scale input signal ranges to the recommended ±512mV full-scale range.

References outside the recommended range may be used with a degradation of linearity. A reference voltage from 200mV to 500mV will result in a lower signalto-noise ratio; a reference voltage from 700mV to 2V will increase the rollover error.

The MAX872 2.50V reference, with its  $10\mu$ A supply current, is ideally suited for the MAX132. Figure 7 shows how 2.50V can be divided to obtain the desired reference voltage. The reference input accepts voltages anywhere within the converter's power-supply range; however, for best performance, neither REF+ nor REF-should come within 2V of the supplies.

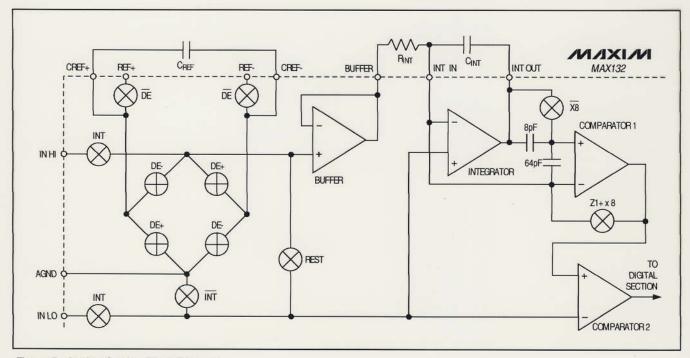

Figure 5. Analog Section Block Diagram

Shaltenstellungen

Dual - Jope ADC

2) integrate down, DE